Policy Information

微机系统的存储器主要可以分成两大类:一类是内部存储器,也称为主存储器,简称为内存和主存;另一类是外部存储器,也称为辅助存储器,简称为外存或赋存。内存由半导体器件构成,分为RAM(随机存取存储器)和ROM(只读存储器)两大类;而我们平常所说的磁盘、光盘、U盘、移动硬盘则属于外存。

在主存储器中,RAM属于易失性存储器,掉电后信息丢失不能恢复;ROM属于非易失性存储器,掉电后信息不丢失,可长期保存,所以一般用来存放固定的程序(系统的引导程序、BIOS等)或重要参数。

今天总结的主要是RAM,分为静态随机存取存储器SRAM、动态随机存取存储器DRAM两种。在整个微机系统存储体系的位置如下图所示。

存储容量:每一个存储芯片能够存储的二进制位数,GB级以上还有TB, PB, EB等单位。

存取速度:从CPU给出有效的存储器地址到存储器输出有效数据所需要的时间,通常以ns为单位。

存储器带宽:存储器每秒传输的数据总量,通常以 B/s 为单位。

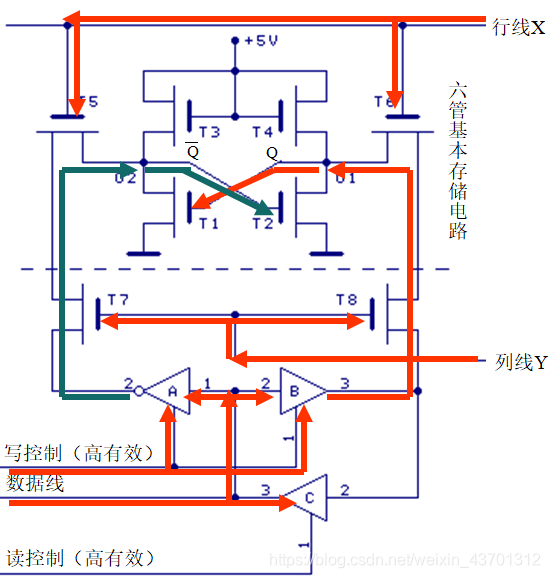

SRAM的基本存储电路内部结构如图所示。其中,上半部分是基本存储单元,用来存储二进制信息0或1;下半部分是读写逻辑单元,由三个三态门、三根信号线和一根数据线组成。

另外,整张图中共有T1~T8八个MOS管,其中T1, T2, T3, T4组成了一个双稳态触发器;T5, T6为行线选通管;T7, T8为列线选通管。当对该存储单元进行读写时意味着该存储单元被选中,故行线X和列线Y为高电平,T5, T6和T7, T8全部导通,因此有了下图的信号流向。 下面假设数据线中为信号1,说明读写时内部电路信号流向(下图中信号线和上面一幅图稍有不同,我们忽略高低电平有效带来的差异,只说控制线是否“有效”)。

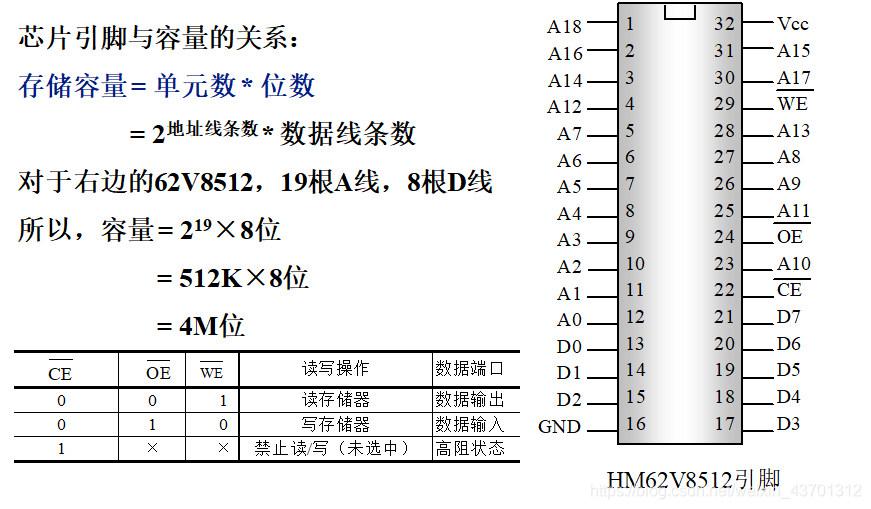

上面讲的是SRAM的基本存储电路,只能存取1位数据,而真正的SRAM芯片则是由多个基本电路以矩阵形式组成的存储阵列,下图是SRAM芯片的一般结构。左边上边是行列译码器,下边是三个控制信号(读、写、片选),右边是一个输出缓冲器。

拿出一块具体的芯片62256来说,就长右边这样:

DRAM看起来就不那么复杂了,下面两图分别是写和读操作的信号流向。

另外,虽然CMOS管是高阻器件,漏电流很小,但是漏电流总是客观存在的,因此C1两端的电荷经过一段时间就会泄露掉,所以不能长时间保存信息。为了维持所存储的信息,必须设法使信息再生,这也就是所谓的“刷新”,同样解释了DRAM为什么叫做动态(Dynamic)随机存取存储器;相比之下的SRAM十分稳定,无需刷新,所以叫做静态(Static)随机存取存储器。

T0管为刷新电路提供信息通道,刷新电路每隔一段时间就会对电容两端的电压进行检测:如果高于Vcc/2,则T0管向位线重新写1从而给C1充电到Vcc;反之,写0使C1放电至0.只要刷新时间满足一定要求,就能保证原有的信息不丢失。

刷新方式主要有三种:集中刷新、分散刷新、异步刷新,这里就不展开讲了。

DRAM的一般结构如下图:

这里值得注意的是,DRAM为了节省外部引脚采用了行选和列选的译码方式,使外部地址线条数只是实际寻址地址线条数的一半。 举个例子:

有很多种改进型DRAM,这里主要提两种。

目前,最新一代的存储器规格是DDR4 SDRAM(可以在京东搜一下QAQ)。

简单列举几种ROM

传统半导体存储器的两大体系:易失性存储器和非易失性存储器。前者例如SRAM、DRAM,虽然数据易失,但是有性能性能高、易用的特点;后者例如各种ROM,虽然断电后数据不丢失,但是都基于ROM技术,具有数据不易写入的缺点。新型的存储器既具有RAM的优点,又具有ROM非易失性特征,同时又可以快速无限次读写,这种新型存储器有铁电式随机存储器(FRAM)和磁阻式随机存储器(MRAM)。

评论